André Martins Pereira

HEP-Frame: a Development Aid and Efficient Execution Engine where a Multi-layer Scheduler Adaptively Orders Pipelined Data Stream Applications

Programa de Doutoramento em Informática (MAP-i) das Universidades do Minho, de Aveiro e do Porto

U. PORTO

Universidade do Minho

Universidade do Minho Escola de Engenharia

André Martins Pereira

HEP-Frame: a Development Aid and Efficient Execution Engine where a Multi-layer Scheduler Adaptively Orders Pipelined Data Stream Applications

Programa de Doutoramento em Informática (MAP-i) das Universidades do Minho, de Aveiro e do Porto

Trabalho realizado sob a orientação do

Professor Doutor Alberto José Gonçalves Carvalho Proença e do

Professor Doutor António Joaquim Onofre de Abreu Ribeiro

### Acknowledgements

First and foremost, I would like to give my deepest gratitude to my supervisors, professors Alberto Proença and António Onofre, for the excellent support, dedication, and more importantly, patience throughout the last seven years we have been working together. To professor Proença, I would like to express my most sincere appreciation for helping me grow as a professional, but above all, as a person, for showing me that I have to put myself and my family first, for guiding me through tough times, and for always fighting to give me the best opportunities I could possibly have. To professor Onofre, I would like to thank for always believing in me, showing the impact that I had on the work of real people even when I doubted myself, and for always being that motivating voice in these last years. I also have to mention that without him I would not try rock climbing, which allowed me to meet the most amazing people that completely changed my life. I hope that this was just the beginning of the collaborations with both of them on a long road ahead.

I would like to give a heartfelt thank to my family, especially to my parents, my brother, and my girlfriend for the endless support, confidence, and happiness throughout the challenges that I had to overcome throughout these years. Without them I could not be where I am today, as they always believed and showed me that I had what it took.

And last, but not least, a sincere thank to all my friends, from inside and outside of the university, who helped me distract from work in many times of stress, while creating the most memorable moments of my life so far. Without them these last years would be so much harder to bear.

Finally, this work is partially funded by FCT - Foundation for Science and Technology, the

Portuguese Ministry of Science, Technology and Higher Education, through national funds, and co-financed by the European Social Fund (ESF) through the Operacional Programme for Human Capital (POCH), with scholarship reference SFRH/BD/119398/2016. This work was developed with support of the computing facilities provided by the project "Search-ON2: Revitalization of HPC infrastructure of UMinho" (NORTE-07-0162-FEDER-000086), co-funded by the North Portugal Regional Operational Programme (ON.2 – O Novo Norte), under the National Strategic Reference Framework (NSRF), through the European Regional Development Fund (ERDF). Additional funding provided under the UTAustin Program, financed by FCT, COMPETE POCI-01-0145-FEDER-007043 within the Project Scope UID/CEC/00319/2013 and by the Laboratório de Instrumentação e Física Experimental de Partículas.

### Abstract

The key component of this thesis work is HEP-Frame, a framework to aid the development and efficient execution of pipelined data stream applications in homogeneous and heterogeneous servers. A pipelined data stream application is a process that converts large amounts of experimental raw data into useful information to monitor data, test hypotheses or validate theories. Each dataset element is then processed by a pipeline of propositions, each containing a computational task that may be followed by an evaluation of a criterion; if this fails the dataset element is removed from the pipeline.

Optimising the computational performance of these applications requires expertise to efficiently vectorize and parallelise the code – namely to take advantage of the vector extensions at each processor (core) and in multiple processors at each server with accelerator devices, in a multi-server cluster – which most scientists lack, or an adequate and easy to use tool or framework, which is nonexistent. With this motivation, the HEP-Frame was designed, implemented and evaluated to provide an user-centred development interface, through the use of code skeletons, automatic code generation, and automation of the compilation process, while transparently scheduling and managing the efficient parallel execution of the code on multicore and manycore servers, with and without accelerator devices.

HEP-Frame implements a multi-layer scheduler that adapts at run-time the application to the computational server(s) and processes the pipeline propositions and various dataset elements in parallel, distributing them across the available computing resources. The top layer balances data and workloads among servers in a heterogeneous cluster environment, using a demand-driven approach to allow HEP-Frame to scale with multiple servers. The middle layer dynamically tunes the number of threads assigned to the parallel data read and setup of adequate data structures, and the pipeline execution. The bottom layer manages the parallel execution of the dataset workload among the available computing resources in a server; this layer includes the reordering of the pipeline propositions of the same dataset element and the parallel execution of multiple dataset elements, ensuring that faster propositions that filter out more data are executed before the more compute intensive propositions.

HEP-Frame also provides a wide range of efficient dual-buffer pseudo-random number generators with uniform or Gaussian distributions, often required by these applications. These can be executed on the compute server, or offloaded to other multicore/manycore servers or to manycore/GPU accelerators. The dual-buffer strategy hides the time penalties to transfer data from other servers or accelerator devices.

The quantitative evaluation of HEP-Frame used three versions of a real world application, the t*ī*H particle physics event data analysis, developed and used by CERN researchers: ttH\_as, ttH\_sci and ttH\_scinp, each with a pipeline with 18 propositions in a default order defined by the developers. The former analysis is latency-bound while the latter two are compute-bound. The t*ī*H analyses are originally sequential, but multithreaded map-reduce parallelisations with OpenMP and StarPU were implemented for thread-by-thread comparison with HEP-Frame. Five heterogeneous servers were selected to perform a quantitative evaluation of the HEP-Frame performance: three dual-socket servers with 12-, 16-, and 24-core Xeon devices (Ivy Bridge, Broadwell, and Skylake, respectively), with the former server being coupled with an NVidia Tesla K20 Kepler GPU and two Intel Xeon Phi Knights Corner devices; a single-socket 10-core Broadwell device coupled with a NVidia GTX 1070 Pascal GPU; and a single-socket 64-core Intel Xeon Phi Knights Landing (KNL) device.

Overall, HEP-Frame improved the performance of the ttH\_as, ttH\_sci and ttH\_scinp applications over their original sequential implementation, by 30x, 252x and 185x on the KNL server and by 32x, 89x and 74x on an Ivy Bridge server with a Kepler GPU. HEP-Frame ensured efficient execution of both memory- and compute-bound pipelined data stream applications portable across various homogeneous and heterogeneous servers with accelerators (in clusters and grid/cloud environments), without requiring any modification of the code, configuration by the user, or prior knowledge of the system characteristics.

### Resumo

A componente chave desta tese é a HEP-Frame, uma framework para ajudar o desenvolvimento e execução eficiente de aplicações de streaming de dados em pipeline para servidores homogéneos e heterogéneos. Uma aplicações de streaming de dados em pipeline é um processo que converte grandes quantidades de dados experimentais em informação útil para monitorizar dados, testar hipóteses ou validar teorias. Cada elemento dos dados é processado por uma pipeline de proposições, em que cada contém uma tarefa computacional que pode ser seguida da avaliação de um critério; se esta falha então o elemento é removido do resto da pipeline.

Otimizar a performance computacional destas aplicações requer perícia para vetorizar e paralelizar eficientemente o código – nomeadamente para tirar partido das extensões vetoriais em cada processador (núcleo) e em múltiplos processadores em cada servidor com aceleradores computacionais, num cluster – que a maior parte dos cientistas não tem, ou de uma ferramenta ou framework adequada fácil de usar, que é inexistente. Com esta motivação, a HEP-Frame foi desenhada, implementada e avaliada para disponibilizar uma interface de desenvolvimento focada no utilizador, através do uso de esqueletos de código, geração automática de código e automatização do processo de compilação, enquanto que gere de forma transparente e eficiente a execução paralela do código em servidores multicore e manycore, com ou sem aceleradores de computação.

A HEP-Frame implementa um escalonador com várias camadas que se adapta às aplicações e aos servidores computacionais em tempo de execução e processa as proposições e vários elementos de dados em paralelo, distribuindo-os entre os recursos computacionais disponíveis. A camada superior distribui os dados e tarefas computacionais entre os servidores num ambiente de cluster heterogéneo, usando uma abordagem demand-driven para permitir que a HEP-Frame escale com múltiplos servidores. A camada intermédia ajusta dinamicamente o número de fios de execução alocados para a leitura e inicialização paralela de dados, e para a execução da pipeline.

A HEP-Frame também disponibiliza uma grande variedade de geradores de números pseudo-aleatórios eficientes em duplo-buffer com distribuições uniformes e Gaussianas, que são normalmente necessários por estas aplicações. Estes podem ser executados nos servidores de computação, ou passados para outros servidores multicore/manycore ou para aceleradores manycore/GPU. A abordagem duplo-buffer esconde os tempos de acesso para transferir dados de e para os outros servidores ou aceleradores.

A avaliação quantitativa da HEP-Frame usou três versões de uma aplicação real, a análise de eventos da física de partículas tīH, desenvolvida e usada por investigadores do CERN: ttH\_as, ttH\_sci e ttH\_scinp, cada com uma pipeline com 18 proposições numa ordem inicial definida pelos programadores. A primeira análise é limitada pela latência da memória enquanto que as restantes são limitadas pela capacidade computacional. As análises tīH são originalmente sequenciais, mas uma paralelizações multifio com OpenMP e StarPU foram implementadas para comparar com a HEP-Frame. Cinco servidores heterogéneos foram selecionados para fazer a avaliação quantitativa da performance da HEP-Frame: três servidores duplo-socket com dispositivos Xeon de 12-, 16-, e 24-núcleos (Ivy Bridge, Broadwell, e Skylake, respetivamente), sendo o primeiro usado em conjunto com um dispositivos GPU NVidia Tesla K20 Kepler e dois Intel Xeon Phi Knights Corner; um servidor de socket único com um dispositivo Broadwell de 10 núcleos com um GPU NVidia GTX 1070 Pascal; e um servidor de socket único Intel Xeon Phi Knights Landing (KNL) com 64 núcleos.

A HEP-Frame melhorou a performance das aplicações ttH\_as, ttH\_sci e ttH\_scinp por 30x, 252x e 185x no servidor KNL e por 32x, 89x e 74x no servidor Ivy Bridge com o GPU Kepler, em relação às suas versões sequenciais. A HEP-Frame garantiu execução eficiente e portável de aplicações de streaming de dados em pipeline limitadas pela memória e pela capacidade computacional em vários servidores homogéneos e heterogéneos com aceleradores (em ambientes cluster e grid/cloud), sem requerer qualquer modificação do código, configuração por parte do utilizador, ou conhecimento prévio das características dos servidores.

# Contents

| 1 | Intr | oducti   | on                                                        | 1  |

|---|------|----------|-----------------------------------------------------------|----|

|   | 1.1  | Motiv    | ation                                                     | 3  |

|   | 1.2  | Contr    | ibutions                                                  | 6  |

|   | 1.3  | Docu     | ment Structure                                            | 7  |

| 2 | Para | allel Co | omputing Environments                                     | 9  |

|   | 2.1  | Homo     | ogeneous Servers                                          | 12 |

|   |      | 2.1.1    | Multicore Devices                                         | 13 |

|   |      | 2.1.2    | Manycore Devices                                          | 15 |

|   | 2.2  | Heter    | ogeneous Servers                                          | 18 |

|   |      | 2.2.1    | Graphics Processing Units                                 | 19 |

|   |      | 2.2.2    | Manycore Coprocessors                                     | 23 |

|   |      | 2.2.3    | Other Hardware Accelerators                               | 25 |

|   | 2.3  | Pipeli   | ned Data Streaming                                        | 26 |

|   |      | 2.3.1    | Computational Characterisation                            | 28 |

|   |      | 2.3.2    | Compute Intensive Tasks                                   | 31 |

|   |      | 2.3.3    | Parallelisation Approaches                                | 33 |

|   | 2.4  | Softw    | are for Efficient Parallel Execution                      | 35 |

|   |      | 2.4.1    | Libraries and Schedulers for Efficient Parallel Computing | 35 |

|   |      | 2.4.2    | Frameworks for Efficient Parallel Computing               | 41 |

|   | 2.5  | Rando    | om Number Generation                                      | 44 |

|   |      | 2.5.1    | Popular PRNG Algorithms                                   | 46 |

|   |      | 2.5.2    | Transforming Uniformly Distributed PRNs                   | 46 |

|   |      | 2.5.3    | PRNG Libraries                                            | 47 |

|   |      |          |                                                           |    |

|   | 2.6 | Sumn   | nary                                                                     | 48  |

|---|-----|--------|--------------------------------------------------------------------------|-----|

| 3 | HEF | P-Fram | e: a Highly Efficient Pipelined Framework                                | 51  |

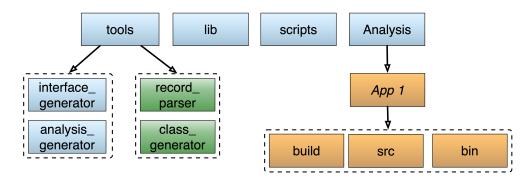

|   | 3.1 | HEP-I  | Frame Structure and Usability                                            | 53  |

|   |     | 3.1.1  | Initial User Interaction                                                 | 54  |

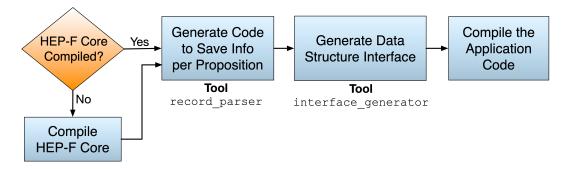

|   |     | 3.1.2  | Tools to Automate the Application Development                            | 56  |

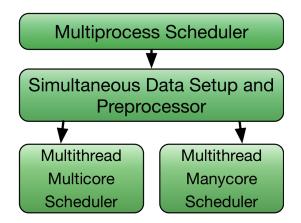

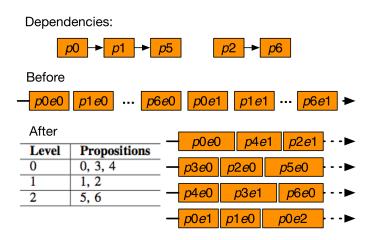

|   | 3.2 | HEP-I  | Frame Multi-layer Scheduler                                              | 59  |

|   |     | 3.2.1  | Structure of the Scheduler Layers                                        | 59  |

|   |     | 3.2.2  | Multiprocess Scheduling                                                  | 60  |

|   |     | 3.2.3  | Dynamic Tuning of Data Setup and Processing                              | 62  |

|   |     | 3.2.4  | Pipeline Ordering and Parallel Execution                                 | 64  |

|   | 3.3 | Using  | Accelerator Devices                                                      | 69  |

|   |     | 3.3.1  | Offloading Propositions into the KNC Coprocessor                         | 70  |

|   |     | 3.3.2  | Offloading PRNGs to Multicore, Manycore and Accelerator Devices $\ldots$ | 72  |

|   |     | 3.3.3  | Pipeline Reordering and Parallelisation in the KNL Server                | 76  |

|   | 3.4 | Sumn   | nary                                                                     | 78  |

| 4 | HEF | P-Fram | e Performance Evaluation                                                 | 81  |

|   | 4.1 | Case S | Studies: $t\bar{t}H$ Scientific Data Analyses                            | 82  |

|   |     | 4.1.1  | The $t\bar{t}H$ Analysis Code                                            | 83  |

|   |     | 4.1.2  | Simple Parallelisation                                                   | 87  |

|   |     | 4.1.3  | Porting $t\bar{t}H$ Analyses into <i>HEP-Frame</i> and StarPU            | 88  |

|   |     | 4.1.4  | Key Characteristics of the $t\bar{t}H$ Analyses                          | 89  |

|   | 4.2 | Testbe | ed and Methodology                                                       | 89  |

|   | 4.3 | Result | ts and Discussion                                                        | 90  |

|   |     | 4.3.1  | Dynamic Tuning of <i>DS</i> and <i>DP</i> Threads                        | 91  |

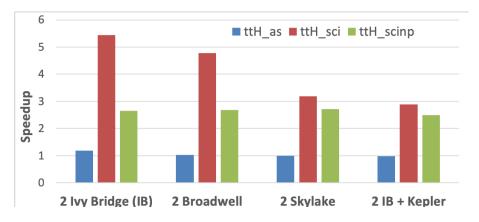

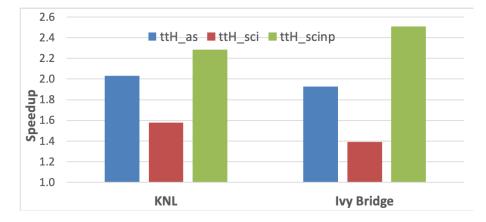

|   |     | 4.3.2  | Multithreading with and Without <i>HEP-Frame</i>                         | 92  |

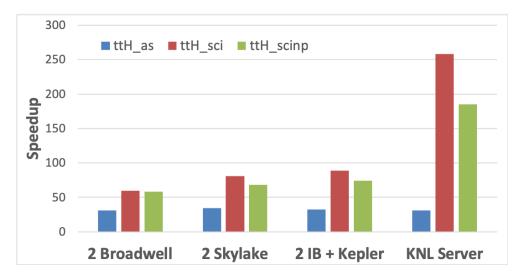

|   |     | 4.3.3  | Multiprocess on Multi-Socket Servers                                     | 95  |

|   |     | 4.3.4  | Proposition Offload to Knights Corner Accelerators                       | 97  |

|   |     | 4.3.5  | Efficient Generation of PRN Batches                                      | 98  |

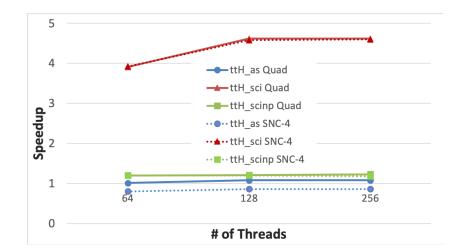

|   |     | 4.3.6  | <i>HEP-Frame</i> in a Manycore KNL Server                                | 104 |

#### CONTENTS

|    |       | 4.3.7  | HEP-Frame vs. StarPU                                         | 107 |

|----|-------|--------|--------------------------------------------------------------|-----|

|    |       | 4.3.8  | Overall Performance <i>vs</i> . the Original Case Studies    | 108 |

|    | 4.4   | Sumn   | nary                                                         | 110 |

| 5  | Con   | clusio | ns and Future Work                                           | 113 |

|    | 5.1   | Futur  | e Work                                                       | 116 |

| Re | ferei | nces   |                                                              | 119 |

| A  | Inst  | alling | and Creating an Application With HEP-Frame                   | 1   |

|    | A.1   | Instal | ling <i>HEP-Frame</i>                                        | 1   |

|    | A.2   | Creati | ng a Pipelined Data Stream Application With <i>HEP-Frame</i> | 2   |

|    |       | A.2.1  | Pipelined Data Stream Application Execution and Output       | 6   |

| B  | HEF   | P-Fram | e API                                                        | 9   |

|    | B.1   | Pseud  | o-Random Number Generation                                   | 9   |

|    | B.2   | Event  | Loading and Output Storage                                   | 11  |

|    | B.3   | Intera | ction with External Libraries                                | 13  |

### CONTENTS

#### CONTENTS

### Glossary

Accelerators hardware to boost the performance of specific computations

Acyclic graph a directional graph with no cycles

- **API** Application Programming Interface, a set of functions to access the functionalities of a given application

- **CUDA** Compute Unified Device Architecture, an API to develop code for CUDA-enabled devices

- DP Data Processing, a task that processes a dataset element

- DS Data Setup, a task that combines input reading, data structure creation, and initialisation

- GPU Graphics Processing Unit accelerator device

- **HEFT** Heterogeneous Earliest Finish Time, an heuristic for load balancing in heterogeneous platforms

Heterogeneous server a server with multicore processing units and accelerators

Homogeneous server a server with multicore processing units

KNC an Intel Xeon Phi manycore co-processor of the Knights Corner micro-architecture

KNL an Intel Xeon Phi manycore server of the Knights Landing micro-architecture

Manycore a specialised processing unit designed for a high degree of parallel processing

Multicore a processing unit with multiple processing cores

Multiprocess code parallelisation that resorts to the use of multiple software processes

- Multithread code parallelisation that resorts to the use of multiple software threads

- **PCI-Express** Peripheral Component Interconnect Express, a high speed bus for computer expansion, such as connecting accelerator devices

- PRNG Pseudo-Random Number Generator

- **Proposition** a computational task that may filter out data from a pipeline

- **Scheduler** a mechanism to manage threads, processes, and workloads across the available computing resources

- SIMD Single Instruction Multiple Data, a parallel microinstruction architecture

- **SMT** Simultaneous Multithreading, multiple hardware threads in a single physical computing core

# **List of Figures**

| 2.1 | Schematic representation of a dual-socket homogeneous server with two mul-         |    |

|-----|------------------------------------------------------------------------------------|----|

|     | ticore CPU devices.                                                                | 13 |

| 2.2 | Schematic representation of the Intel Xeon Phi Knights Landing architecture.       | 16 |

| 2.3 | Schematic representation of a dual-socket heterogeneous server with two mul-       |    |

|     | ticore CPU devices coupled with two accelerator devices.                           | 19 |

| 2.4 | Schematic representation of the NVidia Kepler architecture (obtained from [1]).    | 21 |

| 2.5 | Schematic representation of the Intel Xeon Phi Knights Corner architecture         | 23 |

| 2.6 | Structure of a typical flexible pipelined data stream application using a batch    |    |

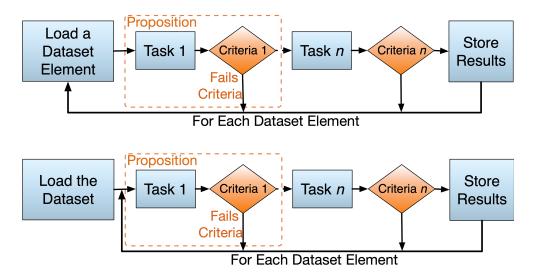

|     | (top) and mini-batch (bottom) input strategies.                                    | 29 |

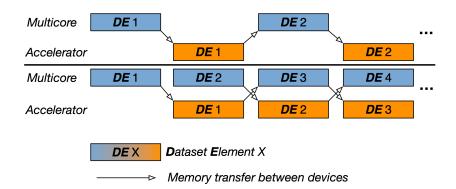

| 2.7 | Processing a dataset element using a simple offload (top) and an interleaved       |    |

|     | offload (bottom).                                                                  | 33 |

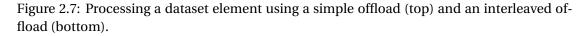

| 2.8 | Schematic representation of the conventional multithread (top) and multipro-       |    |

|     | cess (bottom) parallelisation strategies for scientific code, using 3 threads $tX$ |    |

|     | and processes $pX$                                                                 | 33 |

| 3.1 | Schematic representation of the <i>HEP-Frame</i> directory structure               | 54 |

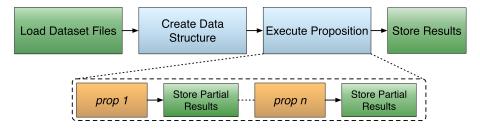

| 3.2 | Execution flow with the HEP-Frame: the user provides code for the darker boxes     |    |

|     | (orange and green) and the framework run-time system manages the blue boxes.       | 56 |

| 3.3 | Multi-layer structure of the <i>HEP-Frame</i> scheduler                            | 60 |

| 3.4 | Sample pipeline execution with the <i>HEP-Frame</i> scheduler                      | 66 |

| 3.5 | Proposition table update as the scheduler moves propositions 4 and 6               | 67 |

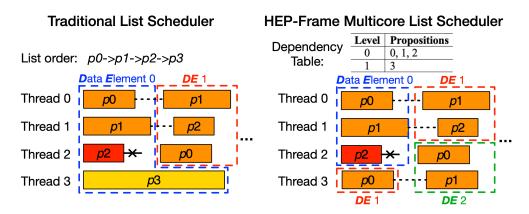

| 3.6  | Typical list scheduler vs. HEP-Frame list scheduler for a pipeline of 4 proposi-                  |     |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | tions with no dependencies                                                                        | 68  |

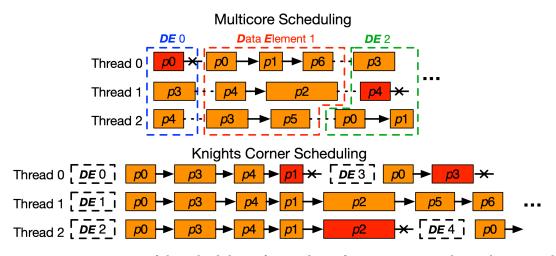

| 3.7  | Comparison of the scheduling of a pipeline of propositions in the multicore and                   |     |

|      | KNC devices                                                                                       | 71  |

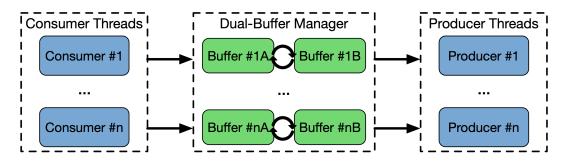

| 3.8  | Dual buffer implementation in the PRNG management threads.                                        | 74  |

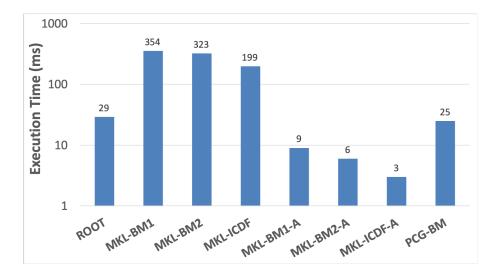

| 3.9  | Sequential execution time of each PRNG implementation for multicore devices                       |     |

|      | to generate 10 <sup>6</sup> PRNs                                                                  | 76  |

| 3.10 | Scheduler pipeline reordering backtracking algorithm for the KNL server                           | 77  |

| 3.11 | Parallel execution of the pipeline in the KNL server for $n$ threads $(Th)$                       | 78  |

| 4.1  | Schematic representation of the $t\bar{t}$ production with an associated Higgs boson,             |     |

|      | in the dileptonic physics channel.                                                                | 84  |

| 4.2  | Schematic representation of the proposition dependencies in $t\bar{t}H$ analysis                  | 85  |

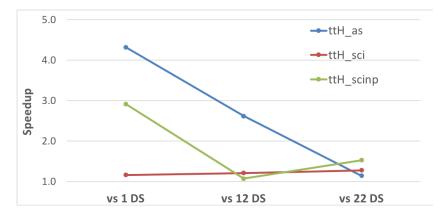

| 4.3  | Speedup of dynamic vs static tuning of DS and DP threads on a dual-socket server.                 | 91  |

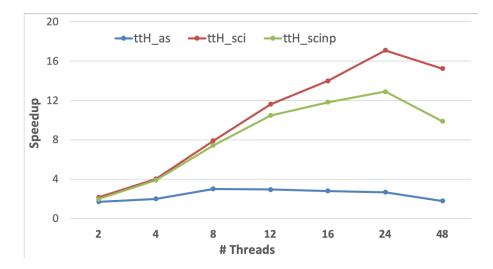

| 4.4  | Scalability of the $t\bar{t}H$ analyses with <i>HEP-Frame</i> on a dual-socket Ivy Bridge server. | 93  |

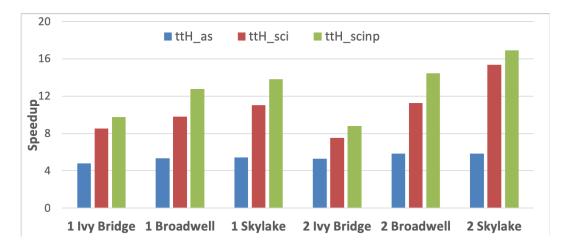

| 4.5  | Speedup of the parallel $t\bar{t}H$ analyses with <i>HEP-Frame vs</i> a standard OpenMP           |     |

|      | parallelisation for the same number of threads on a server with single or dual                    |     |

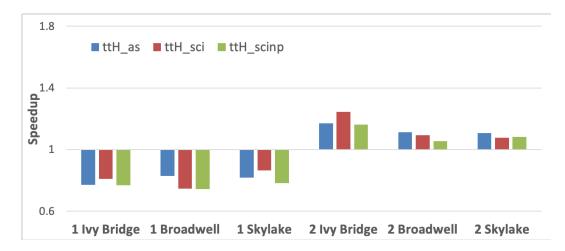

|      | multicore devices                                                                                 | 94  |

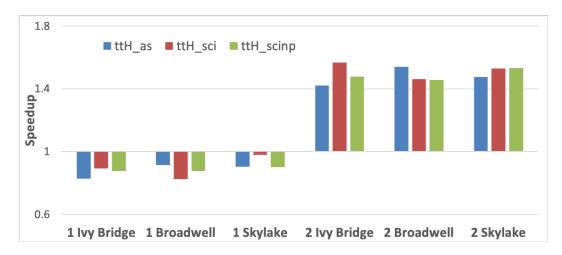

| 4.6  | Comparative performance of a dual process vs. a single process implementa-                        |     |

|      | tion on single and dual socket servers                                                            | 96  |

| 4.7  | Comparative performance of a 4 process vs. a single process implementation                        |     |

|      | on single and dual socket servers.                                                                | 97  |

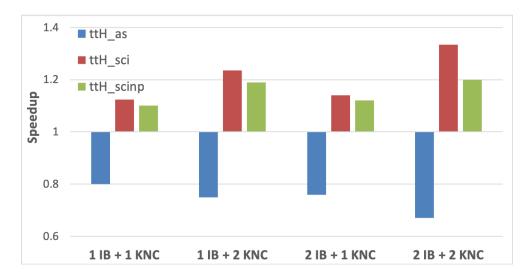

| 4.8  | Speedup of the case studies in a HEP-Frame prototype on a server with one or                      |     |

|      | two Ivy Bridge (IB) devices with KNC accelerators vs the same server without                      |     |

|      | accelerators.                                                                                     | 98  |

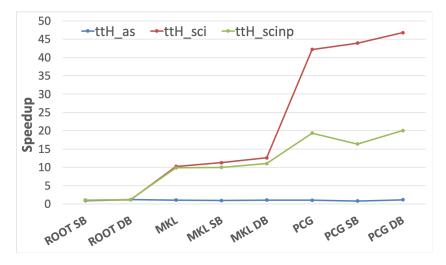

| 4.9  | Speedup of the parallel $t\bar{t}H$ analyses with different PRNG algorithms and ap-               |     |

|      | proaches $vs$ the original ROOT single number PRNG on the Ivy Bridge server                       | 100 |

| 4.10 | Performance comparison of the Broadwell server <i>vs</i> the Ivy Bridge server                    | 101 |

| 4.11 | Speedup of the parallel applications with different PRNG algorithms using ex-           |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | ternal computing devices <i>vs</i> the original ROOT single number PRNG                 | 102 |

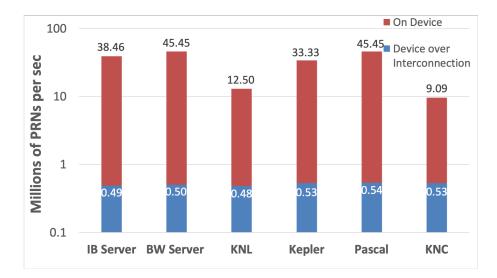

| 4.12 | Throughput of the best PRNG for each different server and accelerator device            | 103 |

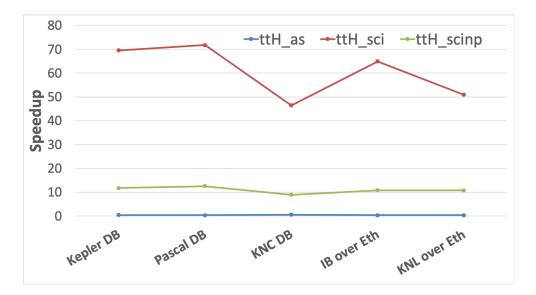

| 4.13 | Speedup of KNL server configurations $vs$ the multicore dual-socket IB server.          | 105 |

| 4.14 | Speedup of the KNL server <i>vs</i> 3 multicore dual-socket servers and a 4th with a    |     |

|      | Kepler GPU                                                                              | 106 |

| 4.15 | Speedup of the case studies for 2, 4 and 6 KNL servers $vs$ a single KNL server         | 107 |

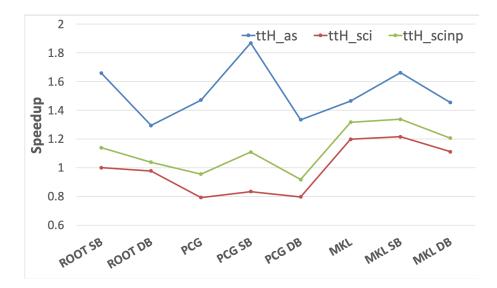

| 4.16 | Speedup of the <i>HEP-Frame</i> scheduler <i>vs</i> the HEFT scheduler in StarPU on the |     |

|      | KNL manycore server and a dual-socket IB server                                         | 108 |

| 4.17 | Overall speedup of the case studies on HEP-Frame vs their original sequential           |     |

|      | implementations                                                                         | 109 |

|      |                                                                                         |     |

| A.1  | The automatic process of compiling a pipelined data stream application in HEP-          |     |

|      | <i>Frame.</i>                                                                           | 4   |

### LIST OF FIGURES

# List of Tables

| 4.1 | Execution time of the 18 propositions in the $t\bar{t}H$ analyses   | 86 |

|-----|---------------------------------------------------------------------|----|

| 4.2 | Filtering ratios of the 18 propositions in the $t\bar{t}H$ analyses | 86 |

### LIST OF TABLES

### **Chapter 1**

## Introduction

This chapter briefly introduces the research field of this dissertation. An overview of the of the parallel computing platforms and the software features relevant for efficient application execution is presented. The key challenges to the development and efficient execution of parallel applications are listed and characterised.

Finally, a list of all the contributions which originated during the development of this dissertation and the structure of this document are presented.

Current large-scale computing platforms are becoming increasingly complex by relying on a large amount of computing servers, each with multiple multicore and/or manycore devices and often coupled with hardware accelerators. The various computational resources available inside a server with wider devices of different micro-architectures need to be adequately used to ensure that applications execute as fast as possible. Mini-clusters are the most popular computing platforms used by the scientific community, which combine a wide variety of desktop and single-node servers. These single-node and desktop servers may be classified as homogeneous, where a server only uses one or multiple multicore devices, or heterogeneous, where one or multiple accelerators are coupled to homogeneous servers using the PCI-Express interface to create a distributed memory environment.

Multicore devices, commonly addressed as CPUs, are becoming increasingly wider for the last decade, where each new chip packs more and more computing cores. For instance, AMD latest server grade multicore device has up to 32 cores (with 2-way simultaneous multithreading per core, SMT), while Intel alternative has up to 28 cores (with 2-way SMT), which can be used in multi-socket servers. The Intel manycore servers, such as the Knights Landing Xeon Phi, provide up to 72 cores with 4-way SMT on a single chip, which reiterates this "more cores per chip" trend. Hundreds of computing cores can be available in a single server, while a few years ago they could only be found in mini-clusters.

Vector computers integrate computing cores based on the Single Instruction Multiple Data (SIMD) architecture, where operations on one-dimensional vectors of independent data are executed by a single instruction. This architecture provides significant performance improvements over scalar processing for specific workloads, and was very popular among supercomputers until the 1990s. Vector computers decrease in popularity was mostly due to its lack of flexibility for general workloads and the drop in the price to performance ratio of conventional processors. Modern multicore devices have a wide variety of SIMD extensions, commonly addressed as vector instructions. It combines the vectorization potential to accelerate specific workloads with the flexibility of conventional multicore devices. While vector instruction sets, such as AVX [2] and 3DNow! [3], do not implement all the features available in the original vector computers, their utilisation is crucial to achieve the full computational

#### 1.1. MOTIVATION

performance available in a server.

A deep knowledge of the underlying architectural details of the computing devices in a server is crucial to develop code that efficiently takes advantage of the available computational resources. It is important to comprehend the key issues that impact the computing performance and efficiency of applications, such as the relationship between the cost of numerical computations, memory accesses and data communications among available computing devices. These issues become imperative when using hardware accelerators, as the architecture of each device is significantly different and often employ distinct programming paradigms.

Developing an efficient parallel application, or adapting existing code, is crucial to ensure that the multiple computing cores in multicore, manycore and accelerators are not used to their full potential. Data races, resource contention, task and data scheduling, and, when considering heterogeneous servers, explicit memory transfers among devices are complex challenges that the programmer must overcome. The tuning of parallel code is often specific to an application on a server, requiring multiple iterative profiling and optimisation time consuming steps by a developer with extensive expertise in high performance computing to achieve good efficiency. These challenges become increasingly complex for non-computer scientists, which develop most of the applications that run on multidisciplinary computing clusters, as they often lack the expertise and/or time to optimise their code. The performance is specially relevant for applications that process large amounts of data, where results must be obtained in a reasonable time frame.

#### 1.1 Motivation

Developing applications that efficiently use the available computational resources in homogeneous and heterogeneous servers requires expertise in high performance computing. The hardware in these servers poses challenges to the programmer that do not appear when developing sequential applications. These challenges become more difficult to overcome by non-computer scientists, which are the developers of a significant amount of the applications that run on high performance cluster environments. Several studies [4, 5, 6, 7] identified the causes that lead non-computer scientists to develop inefficient code:

- Most non-computer scientists are focused on problems relative to their domain of expertise, which leaves little time to develop efficient parallel code.

- Non-computer scientists are not aware of software engineering principles to produce efficient code that is also robust, modular and long lasting.

- Non-computer scientists often iteratively develop over the same application, producing legacy code (some applications currently in production are iterated on for the last 20 years), and not documenting it so that it can be used by others.

- Non-computer scientists are seldom aware of profiling and debugging tools, as well as parallelisation paradigms.

- Non-computer scientists cannot focus on getting into the architectural details of the newer generations of computing devices, reducing the efficiency and portability of their produced code.

One of the most common applications developed by non-computer scientists relate to the analysis of very large sets of experimental data, in a continuous input stream of *n*-tuples, which aim to monitor, test and/or prove hypotheses and theories. The performance of these applications is key to ensure that the large amounts of input data are processed in reasonable time. Most scientific analyses apply a set of pipelined tasks (typically > 10) on independent datasets [8, 9].

An efficient use of computational resources is crucial to significant improve by several orders of magnitude the performance of applications used in several fields of the scientific community. For instance, this is specially important in the high energy physics community at CERN, where a large amount of data needs to be processed by complex analysis applications. The resources expected to become available to process the data gathered in the third and fourth run of the Large Hadron Collider (LHC) will require an increase of the current

computational resources by a factor of 2 to 5 [10]. It is crucial that applications adequately explore the computational resources available in the servers, as buying new hardware no longer guarantees a significant improvement of the performance of applications. Applications must be as efficient as possible in the use of the hardware so that research groups can make an assessment of their limitations and upgrade the hardware accordingly. *HEP-Frame* ensures that pipelined data stream applications can better utilise the available hardware resources, while ensuring that their efficiency is portable across newer hardware generations. The performance improvements already seen from using *HEP-Frame* with existing applications achieve the increased computational throughput required by the third and fourth runs of the LHC, from 2020 to 2029, without the need for additional hardware.

Pipeline stages in data stream applications typically have inter-dependencies and irregular execution times: several are computationally intensive and most filter out irrelevant data elements from further processing. Independent filtering stages can also be commutative. The execution order of the pipeline stages may significantly impact its efficiency, as their individual filtering rates and execution times are different and may change in run-time. This type of applications is also common in fields directly related to computer science, such as query engines and specific data streaming services for embedded and mobile devices [11, 12].

Efficient parallelisations of pipelined data stream applications may be complex to implement, as both task and data parallelism can be explored, and the pipeline execution is irregular. Additionally, the performance of the pipeline varies with different orders of its stages and datasets, which should also be considered by the programmer. An adequate scheduling strategy should analyse all these characteristics of pipelined data stream applications at run-time to provide an efficient workload balance among the computational resources of homogeneous and heterogeneous servers.

Several frameworks and schedulers are available to develop and efficiently execute parallel code for a wide range of applications. However, none of these tools are specifically suited for the characteristics of pipelined data stream applications, which often results in inefficient parallelisations. Additionally, frameworks have steep learning curves and schedulers are not easily integrated into existing parallel code, which may difficult their adoption by computer and non-computer scientists with moderate to low expertise on parallel computing.

This dissertation presents *HEP-Frame*, a framework designed to aid the development and efficient parallel execution of pipelined data stream applications. It provides an easy interface to develop applications, while automating the code generation of simple and repetitive tasks. A multi-layer scheduler transparently manages simultaneous input data setup and processing, parallel execution and reorganisation of the pipeline stages among the available computing resources, and application execution on multiple servers. *HEP-Frame* ensures a more efficient execution of pipelined data stream applications than other alternatives, with no modifications to the user code.

### 1.2 Contributions

Most software tools focus either on improving the performance or the development of specific applications. Tools that focus only on performance are often used in the computer science community, but are rarely adopted by the rest of the scientific community due to their steep learning curves. Tools to aid the development of code are widely used, specially in non-computer science communities, but they are usually computationally inefficient. This dissertation presents *HEP-Frame*, a software tool that aids the development of pipelined data stream applications, while transparently ensuring efficient execution of the code on homogeneous and heterogeneous servers. The goal is to provide a tool that bridges the gap between performance and usability for pipelined data stream applications.

This work presents a multi-layer scheduler with two key novel approaches to task and data balancing. The first is the dynamic tuning of threads assigned to data setup (input load-ing and data structure creation) and to data processing, which allows *HEP-Frame* to automatically adapt at run-time to the requirements of memory- and compute-bound code. The second is the list scheduling of propositions in pipelines, which assigns propositions to threads based on their execution time and filtering ratios, while simultaneously reordering them in order to avoid executing the most computationally complex.

A study on the most efficient approach to manage pseudo-random number generation

is also provided, which exposes the impact that an adequate usage of these algorithms may have on application performance for multicore, manycore and GPU devices. *HEP-Frame* implements the most efficient approaches, which users can access through an API.

The work described in this document is also published in:

- Multi-layer Scheduling with Adaptive Ordering of Pipelined Data Stream Analyses on Heterogeneous Servers - André Pereira and Alberto Proença. Submitted to the *Journal* of Parallel and Distributed Computing.

- **HEP-Frame: a Powerful Tool to Build LHC Data Analyses** André Pereira, António Onofre and Alberto Proença. Submitted to the *European Physics Journal C*.

- Efficient Use of Parallel PRNGs on Heterogeneous Servers André Pereira and Alberto Proença. In *International Conference on Mathematical Applications*, 2018 [13].

- Tuning Pipelined Scientific Data Analyses for Efficient Multicore Execution André Pereira, António Onofre and Alberto Proença. In *Proceedings of the International Conference on High Performance Computing Simulation*, 2016 [14].

- HEP-Frame: A Software Engineered Framework to Aid the Development and Efficient Multicore Execution of Scientific Code - André Pereira, António Onofre and Alberto Proença. In *Proceedings of the 2015 International Conference on Computational Science and Computational Intelligence*, 2015 [15].

- Removing Inefficiencies from Scientific Code: The Study of the Higgs Boson Couplings to Top Quarks - André Pereira, António Onofre and Alberto Proença. In *Proceedings of the 14th International Conference on Computational Science and Its Applications*, 2014 [16].

### **1.3 Document Structure**

This document describes the work accomplished while developing *HEP-Frame*. It is structured as follows:

- **Chapter 1:** presents the context and motivation for the work developed in this dissertation. It describes the challenges to develop efficient pipelined data stream applications and lists the contributions of this work.

- **Chapter 2:** describes the state of the art in a compute server environment. It details the hardware architectures of homogeneous and heterogeneous servers, characterising the relevant performance features of multicore, manycore and accelerator devices. Pipelined data stream applications, the target code of the work in this dissertation, are presented and characterised. Software to develop efficient pipelined code for various computing devices is also presented, with an emphasis on scheduling strategies for the target applications. Finally, efficient implementations of popular pseudo-random number generators are presented, as they often account for a significant execution time of pipelined data stream applications.

- **Chapter 3:** introduces *HEP-Frame*, providing a detailed description of its features to improve the speed of developing efficient pipelined data stream applications, for users with little expertise on parallel computing, and its multi-layer scheduler, which ensures portable efficient execution of these applications on homogeneous and heterogeneous servers.

- **Chapter 4:** discusses the results of a quantitative evaluation of the efficiency features of *HEP*-*Frame* with three real pipelined data stream applications, used in high energy physics, on several servers with various computing devices.

- **Chapter 5:** presents conclusions and identifies future lines of research to further develop the work based on the contributions of this dissertation.

### **Chapter 2**

### **Parallel Computing Environments**

This chapter presents a look into what has been done in the topics related to the work of this dissertation. The first section focus on the current state of the computing hardware available in desktop and cluster environments. The architecture of homogeneous and heterogeneous servers with multicore, manycore and relevant accelerator devices is presented, with an emphasis on key characteristics that should be taken into account when developing efficient parallel code.

Pipelined data streaming, the target application of this dissertation, is presented in detail, with a focus on its structure and computational characteristics that may influence the performance. An overview of common parallelisation approaches used in this type of code by the wider scientific community is also presented.

The relevant software tools and schedulers for efficient code execution in homogeneous and heterogeneous servers are assessed, showing an overview of their approach and possible limitations for pipelined data stream applications. The last Section presents popular PRNG algorithms, detailing their computing characteristics and limitation, as they often account for a significant portion of the pipelined data stream applications execution time. Mini-clusters are the most common computing resource available to scientific research groups. These massively parallel systems are usually constituted by racks of computing nodes (also known as computing servers), interconnected by a low latency network. Each server in a cluster is an individual parallel system that can communicate and share data with other servers. Clusters can be homogeneous or heterogeneous computing platforms, depending on the architectures of their servers. Homogeneous clusters are built with sets of identical servers, such as type of multicore and manycore devices, and amount and speed of RAM. Heterogeneous clusters use servers with different characteristics, usually organised in groups oriented to fulfil specific application requirements. Clusters have also specific servers for centralised high throughput data storage.

Computing servers can also be classified as homogeneous and heterogeneous, depending on the characteristics of their computing devices. Homogeneous servers are single- or multi-socket systems with the same multicore or manycore device in each socket, which share a common memory address space. Heterogeneous servers use single- or multi-socket systems, similarly to homogeneous servers, that couple hardware accelerators to the multicore/manycore devices. This approach combines the flexibility of the main computing devices with the high performance capabilities of manycore devices for specific workloads. However, the multicore and manycore devices do not share a common memory address space with the accelerators, which has to be managed by software. The hardware characteristics of these servers are detailed in sections 2.1 and 2.2.

Pipelined data stream applications continuously execute a pipeline of tasks on large input datasets. This type of applications is common in many scientific fields, and is usually developed by non-computer scientists. The performance of the input pre-processing and the task pipeline has a direct impact on the overall execution time of an application. The development of these applications should take into account strategies to efficiently parallelise their execution to adequately explore the computational resources available in both homogeneous and heterogeneous servers.

The mainstream industry is still adopting the use of multicore architectures with the purpose of increasing their processing performance, which reflects in a lack of academic training on code optimisation and parallel programming. Efficient parallelisation of code for these types of servers requires expertise and time to tune the implementations that most developers lack, specially for servers that combine devices with different architectures and programming paradigms. These factors are specially relevant for non-computer scientists, which are usually self-taught programmers, as they often develop pipelined data stream applications for their researches.

Developing code for homogeneous servers requires knowledge of the underlying hardware architecture of multicore and/or manycore devices and their interconnections. Shared memory, cache coherence and consistency and data races are architecture-specific aspects that the developer does not face in sequential execution environments. However, these concepts are crucial not only to efficiently use the computational resources, but also to ensure the correctness of applications.

Developing code for heterogeneous servers poses additional challenges. Each accelerator device has an unique hardware architecture and programming paradigm designed for a specific workload, which must be mastered to develop code that adequately uses the available resources. For instance, algorithms optimised for multicore execution cannot be easily ported for these devices expecting high performance, and sometimes require a complete re-design of their implementation. Executing an algorithm in multicore/manycore and accelerator devices simultaneously creates an additional layer of complexity, as it requires the implementation of complex workload distribution strategies to ensure that all devices are adequately used.

Several libraries and frameworks are available that are designed to help the parallelisation and workload distribution of data and tasks among the computing devices of homogeneous and heterogeneous servers. Libraries mostly focus on the parallelisation of user-specified sections of an application, requiring minor modifications to the code. They provide simple parallelisation and scheduling techniques that are useful for a wide range of applications. Frameworks target specific types of applications and impose more restrictions to the code structure, such as requiring specific data structures to be used, but provide better computational efficiency. The most relevant libraries and frameworks for efficient code execution on homogeneous and heterogeneous servers are detailed in Section 2.4.

Pseudo-random number generation (PRNG) is a compute intensive task required by most pipelined data stream applications. Popular PRNG algorithms are presented, addressing the different approaches for execution in parallel environments. Several PRNG implementations available in Intel, ROOT, PCG and cuRAND libraries are evaluated on various multicore, manycore and GPU devices in Section 2.5.

#### 2.1 Homogeneous Servers

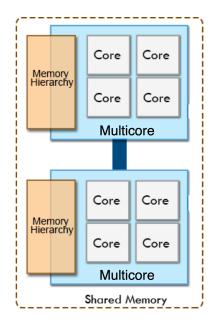

Homogeneous servers are the most common computing platforms used in cluster environments, and contain a single or multiple multicore CPU or manycore devices of the exact same manufacturer and model. Figure 2.1 presents the organisation of a dual-socket homogeneous server. Each device has its own memory hierarchy, which usually contains L1, L2 and L3 caches and a RAM memory bank, and an high bandwidth interface that allows connecting to other devices inside the same server, such as Intel QuickPath Interconnect [17] or AMD Infinity Fabric [18]. Devices in multi-socket server connect to each other using one of these interfaces, which enables sharing of the entire memory hierarchy address space in a Non-Unified Memory Architecture (NUMA).

In a NUMA shared memory address space, a computing core can access data in the memory hierarchy of its device and any other connected device, but with different access latencies. Accessing data in the memory bank of any other device has an increased time penalty as the request and data transfer has to pass through the device interconnection and has to be managed by the memory controller on the other device. Ideally, the threads and/or processes of a parallel application should only access data in their closest memory bank, as accessing data in other memory banks results in an increased time penalty that has an impact on the application execution time.

Figure 2.1: Schematic representation of a dual-socket homogeneous server with two multicore CPU devices.

#### 2.1.1 Multicore Devices

Gordon Moore predicted in 1965 that for the following ten years the amount of transistors on CPU devices would double every 1.5 years [19]. This was later known as the Moore's Law and it remained valid until recently, and meant that smaller and, consequently, more transistors in a chip allowed for an almost linear improvement of the hardware performance. This phenomena created an environment where software developers did not spend much effort optimising the computational efficiency of their applications as the code would get faster due to the incremental improvements of the hardware.

The CPU clock frequency, which has a direct impact on how fast microinstructions are executed, improved linearly until 2005, where thermal dissipation limited further improvements. This lead manufacturers to improve the CPU throughput, rather than their speed, by adding more processing units (known as cores) to a single chip, creating the first multicore devices. These devices had lower clock speeds, as well as energy consumption and operating temperatures, but could execute more microinstructions in each clock cycle. This marked the beginning of the multicore and parallel computing era, where every new generation of CPU devices has a larger throughput, while maintaining the same clock frequencies. However, software developers now have to produce parallel code to take advantage of the multiple computing cores in multicore devices, to ensure efficient execution of applications.

Multicore devices are designed as general purpose computing units based on a set of small processing units attached to a very fast hierarchical memory (cache, whose purpose is to hide the high latency access to global memory). They are capable of delivering a good performance in a wide range of workloads, from executing simple integer arithmetic on scalar values to complex branching and vector processing. A single core implements, at the hardware level, various mechanisms to improve the execution performance of applications. The most relevant to a software developer are:

- **ILP:** Instruction Level Parallelism is the overlapping of microinstructions that would otherwise execute sequentially, and can be performed at both the hardware and software level. At the software level, compilers attempt to identify and group independent instructions that can execute simultaneously, according to the available hardware resources. Developers can expose independent instructions to the compiler by, for instance, overlapping additions and multiplications on independent data, as these instructions can be processed simultaneously by different Arithmetic and Logic Units (ALUs).

- **Vector instructions:** is an extension to an instruction set based on the Single Instruction Multiple Data (SIMD) model, where a single instruction is simultaneously applied to a large set of independent data. Multicore devices have specialised registers and ALUs to execute this type of instructions. Developers can produce vectorized code by using intrinsic instructions of a high level language, which is best suited for complex algorithms, or, in most cases, by indicating to the compiler which sections of the code are suited for automatic vectorization. However, the developer is responsible for assessing that code is adequate to be vectorized, as forcing the vectorization of unsuitable code can cause a degradation in the application performance.

**Simultaneous Multithreading (SMT):** is the hardware support for the execution of multiple threads in a single core of a multicore device, where several threads can run at any given time. This is achieved by replicating part of the core hardware resources, such as registers, to improve the use of the available ALUs in a core. If a piece of code in a hardware thread stalls waiting for data, a second thread is scheduled to execute using the ALUs that would otherwise be idle. SMT can reduce the synchronisation penalties between multiple software threads of an application, as data sharing is faster since they are both executing on the same physical core. The use of SMT can improve the performance of memory intensive applications but hinder compute intensive code, so it is the responsibility of the developer to assess if an application could benefit from this feature.

#### 2.1.2 Manycore Devices

The Intel Many Integrated Core (MIC) architecture, implemented in the Intel Xeon Phi devices, is a manycore device available as either a coprocessor (the Knights Corner architecture) or an autonomous processor (the Knights Landing architecture). The Knights Landing manycore server is based on the Intel Atom Silvermont architecture, with an increased number of cores per device and improved vectorization capabilities over the device it is based on.

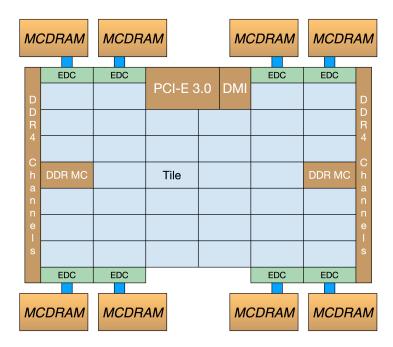

Figure 2.2 presents a schematic representation of the Knights Landing architecture. The micro-architecture of this family offers up to 36 tiles - with two cores per tile, each supporting the simultaneous execution of 4 threads - interconnected by a 2-dimensional mesh. Each core has two 512-bit vector arithmetic units that support most of the AVX-512 instruction set specification, an improvement over the previous iteration of this architecture (Knights Corner). The device has 64 KiB data and 64 KiB instruction caches per core, up to 32 MiB of L2 cache (1 MiB per tile) and access to 384 GiB of DDR4 RAM through eight memory controllers, with a bandwidth of 102 GiB per second.

It has an additional in-package 16 GiB of stacked MCDRAM memory with a bandwidth of 400 GiB per second, which can be configured, according to the specific requirements of each application, as:

Figure 2.2: Schematic representation of the Intel Xeon Phi Knights Landing architecture.

- **Cache:** it acts as a third cache level, and its use does not require any modifications to the application code. Frequent misses on this cache may lead to a decrease in performance. This configuration should not be used for latency-bound applications as preliminary tests show a 20% increase in latency over directly accessing the DDR4 RAM.

- **Flat:** it becomes an addressable Section of the global memory address space. Applications can allocate data structures on this memory by using specific instructions in their code.

- **Hybrid:** it is split evenly between the two previous configurations, with 8 GiB configured as cache and the other 8 GiB as flat memory.

The mesh structure of the cores interconnection allows the user to organise them in different clustering configurations. Each configuration has a direct impact on the cache consistency and coherence protocols, as well as in communication and latency penalties since certain tiles are closer to specific MCDRAM banks than others. The clustering configuration affects both the application parallelisation implementation and its performance:

- **All-to-All:** the whole memory address space shared among all tiles in the device. However, a tile in the middle of the mesh will have higher cache miss penalties than a tile closer to the MCDRAM bank. This configuration also allows sharing data among a large amount of tiles, which can lead to an increased overhead of the cache consistency and coherence protocols.

- **Hemisphere/Quadrant:** divides the tiles into 2 or 4 computing sections of the chip, which are still presented to the user as a single computing device. These sections may share data but the memory controllers only manage their respective Section, which ensures lower L2 cache and MCDRAM miss penalties. Sharing memory among sections has an increased overhead over the All-to-All configuration. Users should code their applications in order to minimise shared data but no major modifications to the code are required.

- **SNC-2/SNC-4:** sub-NUMA cluster partitions the tiles into 2 or 4 independent computing sections of the chip, which are presented to the user as different devices. This reduces cache management overhead and penalties to access MCDRAM, as tiles in a sub-cluster can only share data among each other and access their respective MC-DRAM banks. Communications between clusters must be explicitly coded using a Message Passing Interface [20] library. Users can develop hybrid multithread-multiprocess NUMA-aware code to take advantage of this organisation by pinning processes to certain clusters.

The Knights Landing device uses the same x86 instruction set as conventional multicore devices, which ensures an increased compatibility of applications and libraries. The code still has to be compiled specifically to this architecture to adequately use the AVX-512 vector instruction set. However, the user is still responsible for developing efficient code considering the architecture of this device so that significant performance improvements are obtained, as compilers optimisations are still very limited [21].

# 2.2 Heterogeneous Servers

Heterogeneous servers combine the flexibility of multicore devices with the specialised performance of hardware accelerators in a single system. This type of servers is the most common among general consumers, as most laptop and desktop computers contain a multicore device, used for general computation, coupled with a Graphics Processing Unit (GPU) accelerator, which is specialised for image rendering. Both the scientific community and the industry are adopting this type of servers into their computing clusters due potential of the accelerators to greatly improve the performance of specific workloads.

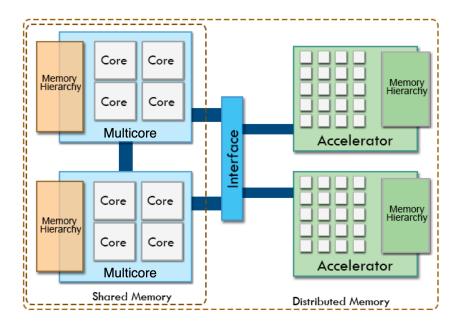

These servers contain one or multiple multicore devices in a shared memory environment, similarly to an homogeneous server, which share a single interface to communicate with any coupled accelerators, as shown in Figure 2.3. Applications must explicitly handle memory transfers between accelerator and multicore devices since the memory address space is distributed. This interface is usually PCI-Express, which has a theoretical peak bidirectional bandwidth of 16 GiB per second for its 3.0 revision [22] (4.0 is available but it is not yet widely adopted). This low bandwidth interface is often a significant bottleneck in applications that regularly communicate with accelerators. The IBM Power9 multicore devices support the NVLink 2.0 interface to directly connect to compatible NVidia GPU devices, offering a bidirectional bandwidth of 150 GiB per second [23], which provides a significant improvement over the PCI-Express interconnection. However, this interface is not supported by other multicore and accelerator device manufacturers.

Accelerator devices are usually built with a large amount of small processing units designed to perform simple operations, as opposed to the large and complex cores found in multicore devices. These devices are best suited for massive parallel problems, where the same instructions are applied to a large amount of independent data (SIMD execution), similarly to vectorization on multicore devices. They are designed to perform these tasks extremely efficiently, freeing the multicore devices to perform more complex computations that may benefit less from such a high degree of parallelisation. Compute intensive tasks such as particle interaction simulation, molecular docking and training and inference of deep neural

Figure 2.3: Schematic representation of a dual-socket heterogeneous server with two multicore CPU devices coupled with two accelerator devices.

networks rely on numerical methods that are processed faster on specific accelerators than on multicore devices.

As of November 2018, 41 of the first 100 clusters on the TOP500 list [24] use either NVidia or Intel accelerator devices, which reiterates the importance of developing efficient code for heterogeneous servers. NVidia GPUs are the most used accelerator, with Kepler, Pascal and Volta based devices on 38 of the top 100 clusters. A similar list focused on consumption efficiency (computing power per Watt) Green500 [25] includes 8 clusters with NVidia GPU accelerators on the top 10. The most popular accelerator devices will be presented through the next subsections.

## 2.2.1 Graphics Processing Units

The Graphics Processing Units (GPUs) are one of the first hardware accelerators generally used to improve the performance of specific workloads. They were initially designed to improve the performance of rendering computer graphics, which started as simple pixel drawing and evolved to support complex 3D scenes that require complex operations, such as transforms, lighting, rasterisation, texturing, depth testing and image display. The GPU architecture is based on the SIMD execution model. Image synthesising is, from the computational point of view, the processing of a large set of values that represent pixels. The processing of each individual pixel usually does not depend on the processing of any other pixel in the image. This allows all pixels in an image to be processed simultaneously by different computing units in the GPU.

Due to the industry demand for customisable shaders, GPUs later allowed some programming flexibility so that developers are able to modify the image synthesis process. Since image synthesis with custom shaders is similar, from the technical perspective, to apply a given algorithm to a 2D matrix, some researchers saw the potential to use these devices to boost the performance of numerical computation. As GPU manufacturers allowed more flexibility to program their devices, the High Performance Computing (HPC) community started to use them to improve the performance of specific massively data parallel problems. The HPC community demand for these devices pushed manufacturers to add features related to numerical computation into GPUs, such as support for double precision floating point arithmetic. This later lead to the creation of GPUs specifically designed for scientific computing.

NVidia is the main GPU manufacturer for scientific computing GPUs, with a wide range of available devices known as Tesla. These devices characteristics differ from general purpose GPUs since they have more GDDR RAM, a different physical design of the printed circuit board to fit in cluster nodes and different cooling options. These chips also have minor architectural modifications, such as more single and double precision processing units and larger memory caches.

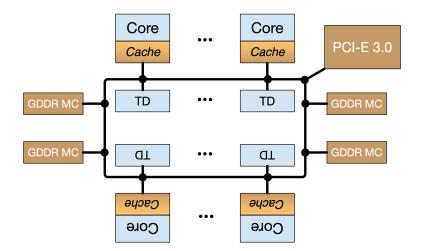

Kepler is the second most common architecture of NVidia GPUs on the Top 500 list [24], and has been used to evaluate the performance of the framework proposed in this dissertation. Figure 2.4 shows the Kepler architecture organisation in two main components: the set of Streaming Multiprocessors (SMX), which can be loosely compared to cores in a multicore device, and the internal memory hierarchy.

There may be up to 15 SMXs in a single chip, which are complex processing units re-

Figure 2.4: Schematic representation of the NVidia Kepler architecture (obtained from [1]).

sponsible for executing the microinstructions in the GPU. Each SMX contains 192 single precision and 64 double precision CUDA cores, small processing units capable of performing basic arithmetic computation, 32 special function units, which perform complex computations such as trigonometric operations, and 32 load and store units. These computing units operate synchronously at the GPU main clock rate.

Each SMX has 64 Ki 32-bit registers, for a maximum of 255 registers per CUDA thread (further detailed in Subsection 2.4.1), a 64 KiB very fast memory for L1 cache and shared memory, and a similar 48 KiB memory cache for read-only data. Finally, the Kepler architecture provides 1.5 MiB of L2 cache shared among all SMX units. The high end Kepler device is the Tesla K80, which has a bandwidth of 280 GiBytes per second to its main memory. The bandwidth for communications between multicore and GPU devices is restricted to only 16 GB/s (8 GB/s in each direction of the channel) by the PCI-Express 3.0 interface.

CUDA threads execute in groups of 32, addressed as a warp, which simultaneously apply the same microinstruction to 32 different data values, using the SIMD execution model. This behaviour is similar to vector instructions used in conventional multicore devices that implement vector extensions to their instruction set.

Kepler implements several features to improve the usage of its computational resources:

- **Dynamic Parallelism:** a kernel (algorithm coded in CUDA) running on the GPU is capable of calling itself recursively, which allows to dynamically generate new workload to process without the CPU interference. This improves irregular algorithms performance on the GPU and reduces the communications to the CPU, as it is capable of adapting to the workload.

- Hyper-Q: this technology increases the amount of work queues to 32 simultaneously hardware managed connections. It allows for multiple cores in a multicore device to launch different kernels on the GPU simultaneously, improving the device resource usage. Multiple threads of an application are able to share the GPU resources and transfer memory simultaneously through independent channels.

- **Grid Management Unit:** allows scheduling multiple grids simultaneously, which allows for different kernels, from possibly different threads, to run concurrently (in combination with Hyper-Q).

- **GPUDirect:** this feature allows GPUs in a single system, or in a interconnected network, to share data without the interference of the CPU and system memory, creating a direct connection to Solid State Drives and other similar devices, reducing the latency of load-ing datasets to its memory.

The most recent NVidia architecture, Volta, provides many improvements over Kepler. It has up to 80 SMX on a single chip, with up to 96 KiB of memory for L1 cache and shared memory, 6 MiB of L2 cache, and a GDDR RAM bandwidth of 900 GiB per second, an improvement from 480 GiB per second in Kepler. It is capable of connecting to multicore devices through either PCI-Express 3.0 or NVLink 2.0.

This architecture supports up to 640 tensor cores per device, which are computing units specifically designed to perform a fused multiply accumulate operations using three 4x4 ma-

trices in a single clock cycle. It also supports half-precision floating point operations, with nearly doubles the throughput over single-precision computation. Both these improvements in the GPU architecture are incredibly useful to improve the performance of algorithms based on matrix-matrix computations, such as neural network training and inference.

## 2.2.2 Manycore Coprocessors

The Intel Xeon Phi manycore coprocessor, Knights Corner architecture, was the first device in the MIC architecture lineup with the purpose of providing a performance similar to the NVidia Tesla devices for scientific workloads. The Knights Corner architecture is schematised in Figure 2.5. The design of Xeon Phi devices has a various key differences from GPUs, as this coprocessor uses fewer computing units that capable of performing more complex operations, and heavily relies on code vectorization. The current high end model, the Intel Xeon Phi 7120p, has 61 cores and 16 GB GDDR5 RAM, which connects to the multicore devices through a PCI-Express 3.0 interface.

Figure 2.5: Schematic representation of the Intel Xeon Phi Knights Corner architecture.

Each core is able to run 4 threads simultaneously, and most of the parallelism is obtained by using the vectorization capabilities provided by the 32 512-bit vector registers and AVX-512 instruction set. However, only a small set of AVX-512 vector operations are implemented in the hardware, with the most complex being emulated by the compiler. This device also does not support out of order execution, which greatly compromises the use of ILP. Each core has 64 KiB + 64 KiB for data + instructions L1 cache, and 512 KiB L2 cache, and there is no shared cache among the 61 cores of the chip. The cores are connected by a bidirectional ring network that does not implement an automatic protocol for cache consistency and coherence.

The Intel Xeon Phi coprocessor supports three operating modes:

- **Native:** the device acts as an independent server, with one core reserved for the operating system execution. The application and all required libraries must be compiled on the host multicore device specifically to run on the coprocessor, copied to the its memory along with the necessary input data, and then executed. No further interaction with the host device is required until the application finishes executing.

- **Offload:** the coprocessor acts as an accelerator, similarly to a GPU. Only part of the application is set to run on the Xeon Phi, as implemented by its developer, and all data required by the code must be explicitly transferred between the host multicore device and the coprocessor. All library functions to be executed inside the coprocessor must be compiled and copied into its memory previous to the application execution.

- **Message passing:** the device acts as an individual computing system in a network. Memory transfers must be handled explicitly and the code should be parallelised using a Message Passing Interface (MPI) implementation [20]. The restrictions mentioned in the previous point are also applicable.

Intel claims that current applications can be easily ported to run on the Xeon Phi coprocessor since it uses the same instruction set as conventional x86 multicore devices. This may be true for simple numerical processing applications, but an efficient port of complex applications that require the use of many external libraries is very difficult, or even unfeasible in some cases [16, 21].

### 2.2.3 Other Hardware Accelerators

Many alternative hardware accelerators are currently available due to the increasing popularity of GPUs and Intel coprocessors in the HPC community. Texas Instruments developed their new line of Digital Signal Processors (DSP) designed for general purpose computing while being very power efficient. They claim that these DSPs are capable of delivering 500 GFlops per second with only a 50 Watt energy consumption [26].

ARM, leaders of the mobile computing industry, are recently developing devices designed for single-node servers in cluster environments <sup>1</sup>. They are being adopted by the HPC community due to their high core count and vector instruction set that support 1024-bit wide vectors with a very low power consumption [27].

Field-programmable gate arrays (FPGAs) are integrated circuits that can be configured by the software developer, using a Hardware Description Language (HDL), resulting in a chip that is designed for a specific algorithm. The first FPGAs contained only a small set of programmable logic units, around 9000, but current versions support up to 50 million, which allows for complex algorithms to be translated into HDL. Currently, these devices are being used as hardware accelerators to improve the performance of specific sections of an application, similar to what GPUs do, as they can offer better performance than multicore devices at a lower clock rate and power consumption [28].

Several devices designed to accelerate specific machine learning tasks, such as training and inference of neural networks, are currently in development and/or production. These devices specialise on high throughput matrix-matrix computations, using with simple memory hierarchies and a low power consumption. The Google Tensor Processing Unit is currently on its second version and is publicly available in Google clusters. This device performs operations on 128x128 single and half precision matrices, with a theoretical performance of 45 TFlops per second [29]. The IBM TrueNorth architecture follows a similar design, where it uses large amounts of simple interconnected cores to simulate neurons [30]. The Intel Nervana architecture provides cores designed for basic matrix operations and convolutions, but

<sup>&</sup>lt;sup>1</sup>e.g. the ARM based Montblanc project will replace the MareNostrum in the Barcelona Supercomputing Center

requires applications to explicitly manage every detail of its memory hierarchy, which reduces the need for memory management hardware and allows more computing cores to be packed in a chip [31].

# 2.3 Pipelined Data Streaming

A pipelined data stream application executes a set of tasks in a sequence to input data in variable sized chunks or datasets, which are previously placed into adequate data structures. Data is usually read by these applications using three different strategies: batch, mini-batch and streaming.

The batch input loads and pre-processes a pre-defined batch of data (usually an input data file) before being available to be processed by the application pipeline code. This is the most commonly used strategy and allows for input reading and initial data setup of different batches to be performed simultaneously. Pipelined data stream applications often explore parallelism by executing multiple binaries of the same application with independent batches, as it is the easiest parallelisation approach to implement.

The mini-batch input loads and pre-processes each individual dataset element, or a small set of elements, from an input batch, which allows data to be earlier available for processing by the application pipeline. However, the most common implementation of this approach relies on reading and processing each dataset element sequentially, which is often stored on global memory without an adequate structure. This approach significantly limits I/O and computing performance as data-level parallelism cannot be explored.

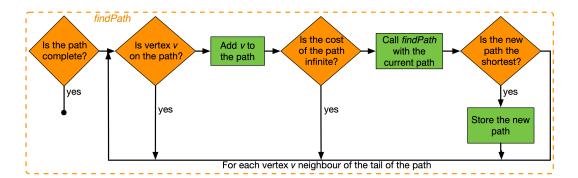

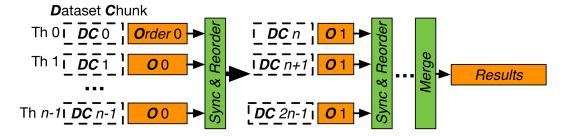

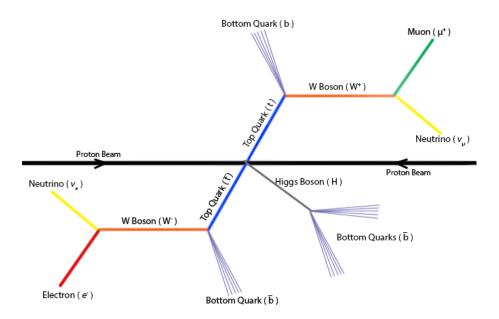

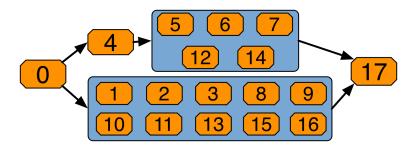

Streaming input continuously loads dataset elements from a given input descriptor, similarly to mini-batch, until it is signalled to stop. This approach differs from mini-batch as in the latter the amount of total data to be read is known in advance. The input data reading, pre-processing and processing have to be managed in run-time, specially when dealing with continuous processing over a large amount of time. Since the overall dataset size is unknown, this approach requires careful memory management and efficient processing of the pipeline, ensuring that both input stream and pipeline computing throughputs are similar, to avoid exceeding the available physical memory.